# **Intel® High Definition Audio Specification**

## **Document Change Notification**

Date: June 6, 2009 Company: Intel Corporation Address: 1900 Prairie City Rd.

City: Folsom State: CA

Country: USA Zip: 95630

Phone:

Change Identification: **DCN No: HDA015-B**

Document Revision: Intel® High Definition Audio 1.0

This document discloses changes to the Intel® High Definition Audio Specification and all information contained herein is provided under the terms of the "AZALIA" SPECIFICATION DEVELOPMENT AGREEMENT" also known as Intel® High Definition Audio Specification Developer Agreement, and all the terms of such agreement, including the confidentiality provisions, shall apply to this disclosure.

# **Title: Low Power Capabilities Clarifications and Enhancements**

## Brief description of the functional changes:

This change of the specification will allow the power to be reduced when devices or the "codec" as a whole is not active. The challenges with the current version of the Intel High Definition Specification include:

- 1) Inability to put the codec into low power state as the ability to report jack presence state changes is not clearly called out and is thus not implemented in typical codecs today

- 2) Clarity for how to use low power states was missing, regarding the reporting of Unsolicited Responses and the ability to wake the system if in low power system states did not exist

- 3) Requirements on what is expected, such as no audio artifacts, and ability to go into low power states was not specified and thus most codecs did not implement sufficient capabilities for states below D0 to be used. As a result, codec low power states were typically not used (were disabled) in the past.

- 4) Lack of clarity on what happens to settings that have been changed across power states and resets.

This set of changes provides a clarification to controlling power at the widget level, adds a requirement to not pop or click when changing power states and also provides for an override function for nodes that support power state controls, but not the Supported Power States parameter.

This set of changes also clarifies the required operation for Jack presence detection and audio streams not coming from or going to the HD Audio link behave during power states other than fully on and during transitions.

In general this set of changes will allow lower power operation to be used by systems and codecs that implement these recommended changes. The changes specified are:

- 1) Codec does not generate spurious sound output on analog outputs such as headphone and speaker jacks during any power state changes.

- 2) Jack Presence state change reporting to operate in all D states except D3cold state of the Pin Widget, Codec in general and the Link power state.

- 3) System wake and reporting of presence, even if the Link clock is not running (Controller low power state)

Intel® High Definition Audio Specification Document Change Notification

Copyright Intel Corporation 2009

- 4) Granular power management

- 5) Time required to exit D3 state back to fully on D0 state set to 10 milliseconds

- 6) Supported Power States command (Verb) is required for all widgets that report PowerCntrl bit set to 1 in their Audio Widget Capabilities response.

- 7) Reduction of D1 and D2 exit times to 1 and 2 milliseconds respectively.

- 8) Inclusion of the ability to reject D3 transition request if not able to due to loop through or other similar activity that the host software is not aware of

- 9) Inclusion of the ability to operate while the clock is stopped and to report that dynamically so that D3 can be used even if there is a chance that prior to stopping the clock, loops through or some other dependency removes the ability. Requires software poll state prior to stopping the clock.

- 10) Clearly state what settable values are reset by POR, Link and Function group resets. Clearly state what settings are persisted across Dx state transitions and Resets. Reporting of any of the settings changes across Dx state through a new status bit also included.

- 11) A new "Double" Function Group capability has been added to guarantee a full initialization of all settings as the settings are no longer initialized for simple Link and Function Group Resets.

- 12) Addition of a new power state that allows the codec to power gate most functionality for the lowest power consumption, thus removing the need for external power FETS for power gating the codec.

## **Current Definitions:**

#### 3.3.16 Offset 30h: Wall Clock Counter

The 32-bit monotonic counter provides a "wall clock" that can be used by system software to synchronize independent audio controllers. The counter must be implemented.

Length: 4 bytes

Table 16. Wall Clock Counter

| Bit  | Type | Reset          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------|------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:0 | RO   | 0000_<br>0000h | Wall Clock Counter (Counter): 32 bit counter that is incremented at the link bit clock rate and rolls over from FFFF_FFFFh to 0000_0000h. This counter will roll over to 0 with a period of approximately 179 seconds with the nominal 24-MHz bit clock rate.  This counter is enabled while the BCLK bit is set to 1. Software uses this counter to synchronize between multiple controllers. The counter will be reset on controller reset. |

. . .

# 5.5.2 Codec Function Group Reset

A codec function group reset allows software to initialize/reset a specific Codec function group without affecting or interrupting the operation of the Link. A codec function group reset is initiated via the Function RESET command verb, as described in Section 7.3.3.33, and results in all logic within the targeted function group being driven to its default or reset state.

#### 5.5.3 Codec Initialization

Immediately following the completion of any reset sequence, all affected Codecs proceed through a codec initialization sequence as described in this section and shown in Figure 30. The purpose of this initialization sequence is to provide each

codec with a unique address by which it can thereafter be referenced with Commands on the **SDO** (broadcast) signal. During this sequence, the Controller provides each requesting codec with a unique address using its attached **SDI** signal(s). Controllers are required to support independent (simultaneous) initialization on all **SDI** signals. Independent initialization allows for codecs to be connected to the interface, be hard reset, and assigned an address even when the link is in normal running state which is required for hot docking.

## 5.6 Power Management

The High Definition Audio Architecture is designed to support all relevant power management features. In most cases, all power management state changes are driven by software, either through controller control registers or Command verbs to codecs. The exception to this is when a codec is put into a low power mode awaiting an external wake up event, such as a ring indication on a modem. In this case, the external wake event results in a power state change request on the Link as described below.

Whenever the Link is commanded to enter a low power state, it enters the link-reset state, as described in Section 5.5.1. This state is only exited in response to a software command and follows all link rules for exiting the link reset state.

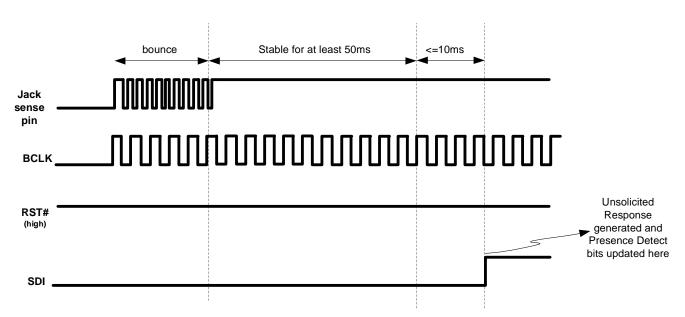

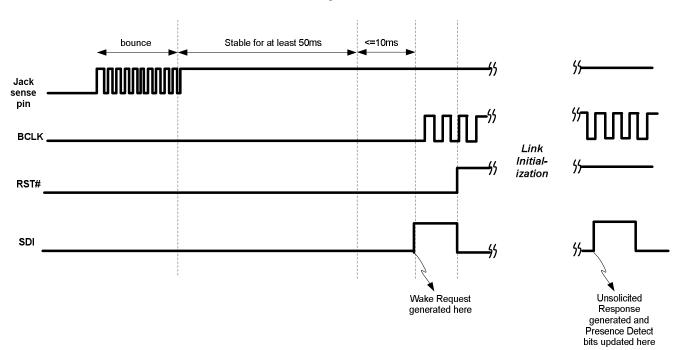

Codecs, when put into a lower power state awaiting an external event, will post the occurrence of a wake event and request a power state change by signaling a power state change request and initialization request as described in Section 5.5.3.1. If **BCLK** and **SYNC** are running at the time of the event, the codec will signal an unsolicited response as described in Section 5.5.3. If **BCLK** and **SYNC** are not running at the time, the codec will signal the power state change request and initialization request asynchronously by asserting **SDI** continuously until it detects the de-assertion of **RST#**, as shown in Figure 33.

#### 7.3.3.10 Power State

The **Power State** control determines the power state of the node to which it refers. There is no required power saving or maximum allowed power in any of the low power states; rather these states allow the vendor to reduce power by as much or as little as desired to meet their customer needs. However, power must never be reduced to a given circuit in a manner that would be inconsistent with the specified power recovery requirements of that power state.

#### **Command Options:**

Table 78 Power State

|     | Verb ID | Payload (8 Bits)                     | Response (32 Bits)                                                |

|-----|---------|--------------------------------------|-------------------------------------------------------------------|

| Get | F05h    | 0                                    | Bits 31:8 are 0<br>PS-Act is in bits 7:4<br>PS-Set is in bits 3:0 |

| Set | 705h    | PS-Set in bits 0:3<br>bits 4:7 are 0 | 0                                                                 |

**PS-Set** is a Power State field which defines the current power setting of the referenced node. If the referenced node is of any type other than a Function Group node, the actual power state is a function of both this setting and the Power State setting of the Function Group node under which the currently referenced node was enumerated (is controlled).

**PS-Act** is a Power State field which indicates the actual power state of the referenced node. Within a Function Group type node, this field will always be equal to the PS-Set field (modulo the time required to execute a power state transition). Within any other type of node, this field will be the lower power consuming state of either a) the PS-Set field of the currently referenced node or b) the PS-Set field of the Function Group node under which the currently referenced node was enumerated (is controlled).

All Power State fields are defined as follows:

#### Power State[1:0]:

**00:** Node Power state (D0) is fully on.

**01:** Node Power state (D1) allows for (does not require) the lowest possible power consuming state from which it can return to the "fully on" state (D0) within 10 ms, excepting analog pass through circuits (e.g., CD analog playback) which must remain fully on.

**10:** Node Power state (D2) allows for (does not require) the lowest possible power consuming state from which it can return to the "fully on" state (D0) within 10 ms. For modems, this is the "wake on ring" power state.

11: Node Power state (D3) allows for (does not require) lowest possible power consuming state under software control. Note that any low power state set by software must retain sufficient operational capability to properly respond to subsequent software Power State command.

PowerState[3:2]: Reserved, always 0.

While Function Group nodes (Audio Function, Modem Function, etc.) and Power Widget nodes must support this control, other widget nodes may optionally implement this control to provide more fine-grained power management of the codec. For Audio Widgets, such as Input Converter or Output Converter Widgets, the Audio Widget Capabilities parameter (see Section 7.3.4.6) will define whether this control is supported.

## **Applies to:**

- (a) Audio Function Group

- (b) Modem Function Group

- (c) Other Function Group

- (d) Power Widget

- (e) Input Converter (Optional)

- (f) Output Converter (Optional)

- (g) Selector Widget (Optional)

- (h) Mixer Widget (Optional)

- (i) Pin Complex (Optional)

• • •

# 7.3.3.13 Pin Widget Control

Pin Widget Control controls several aspects of the Pin Widget.

#### **Command Options:**

Table 1. Enable VRef

|     | Verb ID | Payload (8 Bits)     | Response (32 Bits)                      |

|-----|---------|----------------------|-----------------------------------------|

| Get | F07h    | 0                    | Bits 31:8 are 0<br>Bits 7:0 are PinCntl |

| Set | 707h    | Bits 7:0 are PinCntl | 0                                       |

#### PinCntl format:

| 7      | 6      | 5      | 4:3  | 2:0    |

|--------|--------|--------|------|--------|

| H-Phn  | Out    | In     | Rsvd | VRefEn |

| Enable | Enable | Enable |      |        |

#### Figure 1. PinCntl Format

**H-Phn Enable** disables/enables a low impedance amplifier associated with the output. The value 1 enables the amp. Enabling a non-existent amp is ignored.

**Out Enable** allows the output path of the Pin Widget to be shut off. The value 1 enables the path. Enabling a non-existent amp is ignored.

**In Enable** allows the input path of the Pin Widget to be shut off. The value 1 enables the path.

**VRefEn**: Voltage Reference Enable controls the VRef signal(s) associated with the Pin Widget. If more than one of the bits in the VRef[7:0] field of the Pin Capabilities parameter (Section 7.3.4.9) are non-zero, then this control allows the signal level to be selected.

The VRefEn field encoding selects one of the possible states for the VRef signal(s). If the value written to this control does not correspond to a supported value as defined in the Pin Capabilities parameter, the control must either retain the previous value or take the value of 000, which will put the control in a Hi-Z state and prevent damage to any attached components. Table 2 enumerates the possible values for VRefEn which correlate to the values identified in the Pin Capabilities parameter (see Figure 77).

Table 2. VRefEn Values

| VRefEn Encoding | VREF Signal Level |

|-----------------|-------------------|

| 000b            | Hi-Z              |

| 001b            | 50%               |

| 010b            | Ground (0 V)      |

| 011b            | Reserved          |

| 100b            | 80%               |

| 101b            | 100%              |

| 110b-111b       | Reserved          |

## Applies to:

• Pin Complex

#### • • •

## 7.3.3.9 Digital Converter Control

The **Digital Converter Controls 1** and **2** operate together to provide a set of bits to control the various aspects of the digital portion of the Converter Widget. The S/PDIF IEC Control (SIC) bits are supported in one of two ways. In the first case referred to as "Codec Formatted SPDIF," if a PCM bit stream of less than 32 bits is specified in the Converter Format control, then the S/PDIF Control bits, including the "V," "PRE," "/AUDIO," and other such bits are embedded in the stream by the codec using the values (SIC bits) from the Digital Converter Control 1 and 2. On an input PCM stream of less than 32 bits, the codec strips off these SIC bits before transferring the samples to the system and places them in the Digital Converter Control 1 and 2 for later software access.

In the second case referred to as "Software Formatted (or Raw) SPDIF," if a 32-bit stream is specified in the Converter Format control, the S/PDIF IEC Control (SIC) bits are assumed to be embedded in the stream by software, and the raw 32-bit stream is transferred on the link with no modification by the codec. Similarly, on a 32-bit input stream, the entire stream is transferred into the system without the codec stripping any bits. However, the codec must properly interpret the Sync Preamble bits of the stream and then send the appropriately coded preamble. The IEC60958 specification, Section 4.3, "Preambles," defines the preambles and the coding to be used. Software will specify the "B," "M," or "W" (also known as

"X," "Y," or "Z") preambles by encoding the last four bits of the preamble into the Sync Preamble section (bits 0-3) of the frame. The codec must examine the bits specified and encode the proper preamble based on the previous state. The previous state is to be maintained by the codec hardware. For more information on Preamble Coding, consult Section 4.3 of the IEC 60958 specification.

Table 3. SPDIF Sync Preamble Bits

| Preamble Bits Set by Software (Bits 3:0 of | Preamble Coding    |                    |  |

|--------------------------------------------|--------------------|--------------------|--|

| Frame)                                     | Previous State = 0 | Previous State = 1 |  |

| 1000b ("B" or "Z")                         | 11101000           | 00010111           |  |

| 0010b ("M" or "X")                         | 11100010           | 00011101           |  |

| 0100b ("W" or "Y")                         | 11100100           | 00011011           |  |

#### **Command Options:**

Table 4. S/PDIF Converter Control 1 and 2

|       | Verb ID           | Payload (8 Bits) | Response (32 Bits)                         |

|-------|-------------------|------------------|--------------------------------------------|

| Get   | F0Dh <sup>1</sup> | 0                | Bits 31:16 are 0<br>Bits 15:0 are SIC bits |

| Set 1 | 70Dh              | SIC bits [7:0]   | 0                                          |

| Set 2 | 70Eh              | SIC bits [15:8]  | 0                                          |

| 15   | 14:8    | 7 | 6   | 5      | 4    | 3   | 2    | 1 | 0     |

|------|---------|---|-----|--------|------|-----|------|---|-------|

| Rsvd | CC[6:0] | L | PRO | /AUDIO | COPY | PRE | VCFG | V | DigEn |

Figure 2. S/PDIF IEC Control (SIC) Bits

CC[6:0] (Category Code): Programmed according to IEC standards, or as appropriate.

L (Generation Level): Programmed according to IEC standards, or as appropriate.

PRO (Professional): 1 indicates Professional use of channel status; 0 indicates Consumer.

/AUDIO (Non-Audio): 1 indicates data is non-PCM format; 0 indicates data is PCM.

**COPY** (Copyright): 1 indicates copyright is asserted; 0 indicates copyright is not asserted.

PRE (Preemphasis): 1 indicates filter preemphasis is 50/15 µs; 0 preemphasis is none.

**VCFG** (Validity Config.): Determines S/PDIF transmitter behavior when data is not being transmitted. When asserted, this bit forces the de-assertion of the S/PDIF "Validity" flag, which is bit 28 transmitted in each S/PDIF subframe. This bit is only defined for Output Converters and is defined as Reserved, with a Read Only value of 0 for Input Converters.

- If "V" = 0 and "VCFG"=0, then for each S/PDIF subframe (Left and Right) bit[28] "Validity" flag reflects whether or not an internal codec error has occurred (specifically whether the S/PDIF interface received and transmitted a valid sample from the High Definition Audio Link). If a valid sample (Left or Right) was received and successfully transmitted, the "Validity" flag should be 0 for that subframe. Otherwise, the "Validity" flag for that subframe should be transmitted as "1."

- If "V" = 0 and "VCFG" = 1, then for each S/PDIF subframe (Left and Right), bit[28] "Validity" flag reflects whether or not an internal codec transmission error has occurred. Specifically, an internal codec error should result in the "Validity" flag being set to 1. In the case where the S/PDIF transmitter is not receiving a sample or does not receive a valid sample from the High Definition Audio Controller (Left or Right), the S/PDIF transmitter should set the S/PDIF "Validity" flag to 0 and pad each of the S/PDIF "Audio Sample Word" in question with 0's for the subframe in question.

\_

<sup>&</sup>lt;sup>1</sup> The Verb Code F0Eh is reserved for S/PDIF Converter Control 2 and may never be reassigned to anything else. However, it need not be implemented since standard software drivers must never use it. If a codec elects respond to this code, the response must be identical in all respects to the response to Verb Code F0Dh.

If a valid sample (Left or Right) was received and successfully transmitted, the "Validity" flag should be 0 for that subframe.

If "V" = 1 and "VCFG" = 0, then each S/PDIF subframe (Left and Right) should have bit[28] "Validity" flag = 1. This tags all S/PDIF subframes as invalid.

"V" = 1 and "VCFG" = 1 state is reserved for future use.

Default state, coming out of reset, for "V" and "VCFG" should be 0 and 0 respectively.

${f V}$  (Validity): This bit affects the "Validity flag," bit[28] transmitted in each subframe, and enables the S/PDIF transmitter to maintain connection during error or mute conditions. The behavior of the S/PDIF transmitter with respect to this bit depends on the value of the "VCFG" bit.

**DigEn** (Digital Enable): Enables or disables digital transmission through this node. A 1 indicates that the digital data can pass through the node. A 0 indicates that the digital data is blocked from passing through the node, regardless of the state. **Applies to:**

Input Converter

Output Converter

#### 7.3.3.29 Volume Knob

**Volume Knob** provides the controls for an optional external hardware volume control.

#### **Command Options:**

Table 5. Volume Knob Control

|     | Verb ID | Payload (8 Bits)                      | Response (32 Bits)                    |

|-----|---------|---------------------------------------|---------------------------------------|

| Get | F0Fh    | 0                                     | Bit 7 is Direct<br>Bits 6:0 is Volume |

| Set | 70Fh    | Bit 7 is Direct<br>Bits 6:0 is Volume | 0                                     |

**Direct** causes the Volume Control Widget to directly control the hardware volume of the slave amplifiers. If "Direct" is set to a 0, the volume control will not directly affect the volume of the slaves amplifiers; rather, the software receives an unsolicited response, reads the volume control, and then programs the appropriate amplifiers correctly.

**Volume** is specified in steps, as is amplifier gain. If two amplifiers slaved to the Volume Knob control have different "StepSize" parameters, they are both adjusted by the same number of steps, implying a differing total dB treatment. If the Volume Knob control has more steps than a slave amplifier is capable of supporting (as indicated in the Volume Knob Capabilities parameter), the amplifier remains at its limiting value.

#### **Applies to:**

• Volume Knob Widget

• • •

#### 7.3.3.33 Function Reset

The **Function Reset** command causes the functional unit, and all widgets associated with the functional unit, to return to their power-on reset values. Note that some controls such as the Configuration Default controls should not be reset with this command. It is also possible that certain other controls, such as Caller-ID, should not be reset.

This command does not affect the Link interface logic, which must be reset with the link **RST**# signal. Therefore, a codec must not initiate a Status Change request on the link.

When a codec receives the Function reset verb, the expected behavior is that the codec will issue a response to the verb to acknowledge receipt, and then reset the affected Function Group controls. The codec must be ready to respond to the verbs on the Link frame after the frame on which it returns its response to the Reset command.

#### **Command Options:**

Table 108. Function Reset

|         | Verb ID | Payload (8 Bits) | Response (32 Bits) |

|---------|---------|------------------|--------------------|

| Execute | 7FFh    | 0                | 0                  |

#### Applies to:

- (a) Audio Function Group

- (b) Modem Function Group

- (c) Other Function Group

• • •

# 7.3.4.12 Supported Power States

Returns a bit field describing the power states supported by the functional unit and widgets.

**Parameter ID:** 0Fh **Response Format:**

| 31:8     | 3     | 2     | 1     | 0     |

|----------|-------|-------|-------|-------|

| Reserved | D3Sup | D2Sup | D1Sup | D0Sup |

Figure 80. Supported Power States Response Format

## **Applies to:**

- (a) Audio Function

- (b) Modem Function

- (c) Other Functions

- (d) Power Widget

- (e) Other Widgets (optional)

## **New Definition:**

#### 3.3.16 Offset 30h: Wall Clock Counter

The 32-bit monotonic counter provides a "wall clock" that can be used by system software to synchronize independent audio controllers. The counter must be implemented.

Length: 4 bytes

Table 16 Wall Clock Counter

| Bit  | Type | Reset          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------|------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:0 | RO   | 0000_<br>0000h | Wall Clock Counter (Counter): 32 bit counter that is incremented at the link bit clock rate and rolls over from FFFF_FFFFh to 0000_0000h. This counter will roll over to 0 with a period of approximately 179 seconds with the nominal 24-MHz bit clock rate.  This counter will only operate (count) while the BitClk on the link for this controller is running. During low power states of the controller the clock may not be running and thus software should not assume that the counter continued to increment across Dx states and re-synchronize once the controller returns to the D0 state. Software uses this counter to synchronize between multiple controllers. The counter will be reset by controller reset. |

• • •

# 5.5.2 Codec Function Group Reset

A codec function group reset allows software to initialize/reset a specific Codec function group without affecting or interrupting the operation of the Link. A codec function group reset is initiated via the Function RESET command verb, as described in Section 7.3.3.33, and results in all logic within the targeted function group being driven to its default or reset state. For codecs that report Extended Power States Supported of one (1) this Function Reset does not initialize some of the settings that are programmable by host software. Which settings are persisted is defined in Table T2. Host software may send two Function Resets (possibly separated by an undefined number of idle frames, but no other valid commands), which shall cause a full reset of all settings. For more information, see Section 7.3.3.33.

A single or double Function Group reset <u>does not</u> cause the codec to perform the "Codec Initialization request" sequence defined in section 5.5.3.

#### 5.5.3 Codec Initialization

Immediately following the completion of Link Reset sequence or when requesting a power state change when the link is in a low power state, all affected Codecs proceed through a codec initialization sequence as described in this section and shown in Figure 30. The purpose of this initialization sequence is to provide each codec with a unique address by which it can thereafter be referenced with Commands on the **SDO** (broadcast) signal. During this sequence, the Controller provides each requesting codec with a unique address using its attached **SDI** signal(s). Controllers are required to support independent (simultaneous) initialization on all **SDI** signals. Independent initialization allows for codecs to be connected to the interface, be hard reset, and assigned an address even when the link is in normal running state which is required for hot docking. A codec in a low power state (D1 through D3 and D3cold) retains its address while in that low power state. If the link is in reset and the codec requests a power state change back to fully powered (D0), it is required for the codec to reestablish the connection with the controller by performing a "Codec Initialization request" as specified in this section. During link initialization, the controller shall assign to the codec the same address that the codec had prior to the link being reset, as long as the codec remains on the same SDI line.

• • •

## 5.6 Power Management

The High Definition Audio Architecture is designed to support all relevant power management features. In most cases, all power management state changes are driven by software, either through controller control registers or Command verbs to codecs. The exception to this is when a codec (Function Group) is put into a low power mode either waiting for an external wake up event, such as a ring indication on a modem or a state change that requires that the codec be placed into D0 (Fully powered) such as Jack Presence Detection change for an Audio Codec's attached device or a Modem Codec's ring detection. In this case, the external event results in a power state change request on the Link as described below.

Whenever the Link is commanded to enter a low power state, it enters the link-reset state, as described in Section 5.5.1. This state is only exited in response to a software command and follows all link rules for exiting the link reset state.

Codec's Function Group, when put into a lower power state where the Function Group may need to return to D0 (Fully Powered), will post the occurrence of a wake event and request a power state change by signaling a power state change request and if necessary, based on link power state, an initialization request as described in Section 5.5.3.1. If BCLK and SYNC are running at the time of the event, the codec will signal an unsolicited response. If BCLK and SYNC are not running at the time, the codec will signal the power state change request and initialization request asynchronously by asserting SDI continuously until it detects the de-assertion of RST#, as shown in Figure 33.

• • •

## 7.3.3.9 Digital Converter Control

The **Digital Converter Controls 1, 2, 3 and 4** operate together to provide a set of bits to control the various aspects of the digital portion of the Converter Widget. The S/PDIF IEC Control (SIC) bits are supported in one of two ways. In the first case referred to as "Codec Formatted SPDIF," if a PCM bit stream of less than 32 bits is specified in the Converter Format control, then the S/PDIF Control bits, including the "V," "PRE," "/AUDIO," and other such bits are embedded in the stream by the codec using the values (SIC bits) from the Digital Converter Control 1 and 2. On an input PCM stream of less than 32 bits, the codec strips off these SIC bits before transferring the samples to the system and places them in the Digital Converter Control 1 and 2 for later software access.

In the second case referred to as "Software Formatted (or Raw) SPDIF," if a 32-bit stream is specified in the Converter Format control, the S/PDIF IEC Control (SIC) bits are assumed to be embedded in the stream by software, and the raw 32-bit stream is transferred on the link with no modification by the codec. Similarly, on a 32-bit input stream, the entire stream is transferred into the system without the codec stripping any bits. However, the codec must properly interpret the Sync Preamble bits of the stream and then send the appropriately coded preamble. The IEC60958 specification, Section 4.3, "Preambles," defines the preambles and the coding to be used. Software will specify the "B," "M," or "W" (also known as "X," "Y," or "Z") preambles by encoding the last four bits of the preamble into the Sync Preamble section (bits 0-3) of the frame. The codec must examine the bits specified and encode the proper preamble based on the previous state. The previous state is to be maintained by the codec hardware. For more information on Preamble Coding, consult Section 4.3 of the IEC 60958 specification.

Table 6. SPDIF Sync Preamble Bits

| Preamble Bits Set by Software (Bits 3:0 of | Preamble Coding    |                    |  |

|--------------------------------------------|--------------------|--------------------|--|

| Frame)                                     | Previous State = 0 | Previous State = 1 |  |

| 1000b ("B" or "Z")                         | 11101000           | 00010111           |  |

| 0010b ("M" or "X")                         | 11100010           | 00011101           |  |

| 0100b ("W" or "Y")                         | 11100100           | 00011011           |  |

#### **Command Options:**

Table 7. S/PDIF Converter Control 1, 2, 3 and 4

|       | Verb ID           | Payload (8 Bits)        | Response (32 Bits)                                    |

|-------|-------------------|-------------------------|-------------------------------------------------------|

| Get   | F0Dh <sup>2</sup> | 0                       | Bits 31:24, 22:20, 15 are 0<br>Bits 31:0 are SIC bits |

| Set 1 | 70Dh              | SIC bits [7:0]          | 0                                                     |

| Set 2 | 70Eh              | SIC bits [15:8]         | 0                                                     |

| Set 3 | 73Eh              | 73Eh SIC bits [23:16] 0 |                                                       |

| Set 4 | 73Fh              | SIC bits [31:24]        | Rsvd 0                                                |

| 31:24 | 23                      | 22:20 | 19:16                 | 15   | 14:8    | 7 | 6   | 5      | 4    | 3   | 2    | 1 | 0     |

|-------|-------------------------|-------|-----------------------|------|---------|---|-----|--------|------|-----|------|---|-------|

| Rsvd  | Keep<br>Alive<br>Enable | Rsvd  | IEC<br>Coding<br>Type | Rsvd | CC[6:0] | L | PRO | /AUDIO | COPY | PRE | VCFG | V | DigEn |

Figure 3. S/PDIF IEC Control (SIC) Bits

**KeepAlive** (Keep Alive Enable): this bit is applicable only to digital converter widget that is associated (selected by) an Output Digital Pin Widget. This bit allows for software programmed control of S/P-DIF, HDMI and Display Port interfaces to continue to provide clocking information to an attached device. Many such digitally connected audio devices can take more than one second to start playing audio after the clock has stopped, which occurs for example when the Converter and/or Digital Pin Widget is placed into a low power state or even just when a stream is stopped for S/P-DIF. Although this capability is more closely associated with the output port and thus the converter widget, the generation of a valid digital stream and clock is normally provided by the Converter Widget and thus this functionality is included here. Support for the **KeepAlive Enable** is mandatory after July 1st 2011, if EPSS is reported set to 1. When **KeepAlive Enable** is set to 1 the output will supply a continuous clock, and a valid but 'silent' data stream, even when no stream is selected by this Converter Widget and while the Digital Converter and/or Digital Pin Widget connected to this Converter Widget is in D0-D3<sup>3</sup>. If D3cold state is supported, then the "Keep Alive" shall not be operational while in the D3cold state.

When the output from the Pin Widget connected to this Converter Widget is connected to a combination electrical and optical (TOSLINK) jack, the jack-detection capability of the electrical 3.5mm jack must also be used to report Presence Detection in the Digital Pin Widget associated with this Digital Converter's S/P-DIF output, and must also support an unsolicited response generation when the jack state changes. It is recommended that driver software disable the keep alive bit when the output port is not connected and enable it when the output port is connected to reduce the power consumed during idle. It is also recommended that driver software disable the keep alive bit when the associated output port is connected but when the Optical S/P-DIF output is not the default output device.

As mentioned above, the Keep Alive Enable bit is not applicable to input converters of digital ports. In the case of an input port, the driver software should periodically (e.g. every few seconds) wake up the Function Group out of D3 state and poll the port to see if it has locked to an input stream. If the input port is connected to a combo jack, jack-detection capability must be supported and an unsolicited response must be generated when the jack state changes. In that case, software will have to periodically poll for lock status only when it knows that the port is connected to an external transmitter.

\_

<sup>&</sup>lt;sup>2</sup> The Verb Code F0Eh is reserved for S/PDIF Converter Control 2 and may never be reassigned to anything else. However, it need not be implemented since standard software drivers must never use it. If a codec elects respond to this code, the response must be identical in all respects to the response to Verb Code F0Dh.

<sup>&</sup>lt;sup>3</sup> It is likely that an output s/pdif data stream cannot be generated, unless the HD Audio link clock is running. In that case, if the s/pdif output ports must be kept alive in D3 state, the bus link clock will have to not be allowed to turn off when in the CODEC is placed in D3 state

**IEC Coding Type [3:0]** (IEC Coding Type): Programmed according to IEC standards to enable stream types for High Bit Rate Encoding. This is valid only for HDMI and Display port digital Pin Widgets.

CC[6:0] (Category Code): Programmed according to IEC standards, or as appropriate.

L (Generation Level): Programmed according to IEC standards, or as appropriate.

**PRO** (Professional): 1 indicates Professional use of channel status; 0 indicates Consumer.

/AUDIO (Non-Audio): 1 indicates data is non-PCM format; 0 indicates data is PCM.

**COPY** (Copyright): 1 indicates copyright is asserted; 0 indicates copyright is not asserted.

PRE (Preemphasis): 1 indicates filter preemphasis is 50/15 µs; 0 preemphasis is none.

**VCFG** (Validity Config.): Determines S/PDIF transmitter behavior when data is not being transmitted. When asserted, this bit forces the de-assertion of the S/PDIF "Validity" flag, which is bit 28 transmitted in each S/PDIF subframe. This bit is only defined for Output Converters and is defined as Reserved, with a Read Only value of 0 for Input Converters.

- If "V" = 0 and "VCFG"=0, then for each S/PDIF subframe (Left and Right) bit[28] "Validity" flag reflects whether or not an internal codec error has occurred (specifically whether the S/PDIF interface received and transmitted a valid sample from the High Definition Audio Link). If a valid sample (Left or Right) was received and successfully transmitted, the "Validity" flag should be 0 for that subframe. Otherwise, the "Validity" flag for that subframe should be transmitted as "1."

- If "V" = 0 and "VCFG" = 1, then for each S/PDIF subframe (Left and Right), bit[28] "Validity" flag reflects whether or not an internal codec transmission error has occurred. Specifically, an internal codec error should result in the "Validity" flag being set to 1. In the case where the S/PDIF transmitter is not receiving a sample or does not receive a valid sample from the High Definition Audio Controller (Left or Right), the S/PDIF transmitter should set the S/PDIF "Validity" flag to 0 and pad each of the S/PDIF "Audio Sample Word" in question with 0's for the subframe in question. If a valid sample (Left or Right) was received and successfully transmitted, the "Validity" flag should be 0 for that subframe.

- If "V" = 1 and "VCFG" = 0, then each S/PDIF subframe (Left and Right) should have bit[28] "Validity" flag = 1. This tags all S/PDIF subframes as invalid.

- "V" = 1 and "VCFG" = 1 state is reserved for future use.

Default state, coming out of reset, for "V" and "VCFG" should be 0 and 0 respectively.

**V** (Validity): This bit affects the "Validity flag," bit[28] transmitted in each subframe, and enables the S/PDIF transmitter to maintain connection during error or mute conditions. The behavior of the S/PDIF transmitter with respect to this bit depends on the value of the "VCFG" bit.

**DigEn** (Digital Enable): Enables or disables digital transmission through this node. A 1 indicates that the digital data can pass through the node. A 0 indicates that the digital data is blocked from passing through the node, regardless of the state. **Applies to:**

Input Converter

Output Converter

#### 7.3.3.10 Power State

The **Power State** control determines the power state of the node to which it refers. There is no required power saving or maximum allowed power in any of the low power states; rather these states allow the vendor to reduce power by as much or as little as desired to meet their customer needs. However, power must never be reduced to a given circuit in a manner that would be inconsistent with the specified power recovery requirements of that power state.

It is required that no anomalous sounds be generated by any node while it is transitioning between power states. For example no Pop or Clicks should be generated on an output port during D0 to D3 or other states and visa versa. If Pops or Clicks are produced during power state transitions, then the codec must suppress these without any software directed action, other than the power state control change. This applies to audio or modem codecs or other codecs which generate analog audio output.

#### **Command Options:**

Table 78 Power State

|     | Verb ID | Payload (8 Bits)                                  | Response (32 Bits)            |

|-----|---------|---------------------------------------------------|-------------------------------|

| Get | F05h    | 0                                                 | Bits 31:11 are 0 and reserved |

|     |         |                                                   | PS-SettingsReset is in bit 10 |

|     |         |                                                   | PS-ClkStopOk is in bit 9      |

|     |         |                                                   | PS-Error is in bit 8          |

|     |         |                                                   | PS-Act is in bits 7:4         |

|     |         |                                                   | PS-Set is in bits 3:0         |

| Set | 705h    | PS-Set in bits 0:3<br>bits 4:7 are Reserved and 0 | 0                             |

**PS-Set** is a Power State field which defines the current power setting of the referenced node. If the referenced node is of any type other than a Function Group node, the actual power state is a function of both this setting and the Power State setting of the Function Group node under which the currently referenced node was enumerated (is controlled).

**PS-Act** is a Power State field which indicates the actual power state of the referenced node. Within a Function Group type node, this field will always be equal to the PS-Set field (modulo the time required to execute a power state transition, if currently in transition from a lower to higher power consuming state or from a higher power consuming state to D3cold). Within any other type of node, this field will be the lower power consuming state of either the currently referenced node or the Function Group node under which the currently referenced node was enumerated (is controlled).

**PS-Error** is reported as set to 1, when the power state requested by the host is not possible at this time. This may occur if there are dependencies between nodes that require both to be in D0 for proper operation or in cases where some operation that the host is unaware of, prohibits entering the D3 state. If the node responds to a Set Power State verb by setting the PS-Error bit to '1', then the node will remain in its previous power state at least until it receives the next Set Power State verb. If the node is going to remain in its previous power state, it shall set the PS-Error bit immediately, so it can be read by software in the next frame. If the node does not set the PS-Error bit after it receives a Set Power State verb, then it will transition to the commanded state (even though it may or may not allow for the link clock to turn off, as explained below). In all cases the reported states for Active and Set states will report both the requested and the actual power state. Note, however, that the latency from receiving the Set Power State verb to PS-Act getting updated to reflect the new state depends on the hardware implementation, so testing whether PS-Act is equal to PS-Set is not a safe way to determine whether the node was able to transition to the commanded power state or not. PS-Error should be used for that.

If a widget is commanded to a power state that it can not transition to and the widget responds by setting PS-Error, this will not affect the PS-Error bit of the Function Group that the widget belongs to. If, however, a widget is indirectly requested to transition to a lower power dissipating state because its Function Group has been commanded to that state and the widget can not transition to that state, then the PS-Error bit of both the widget and the Function Group will be set and the power state of both will not change.

**PS-** ClkStopOk is reported when the codec is capable of continuing proper operation even when the clock has been stopped. This bit is applicable at the Function Group level and is reserved at the widget-level. It is required for the codec to support the Get Power State commands after being commanded to enter the D3 state and report the ability for operation with the clock stopped. Reporting this while in other Dx states is optional.

The bus clock should not stop at a time when ClkStopOk is reported as '0'. However, if the bus clock does stop, then a full reset shall be performed.

Strategies for using PS-Error and PS-ClkStopOk:

There are some cases where there are power dependencies that are not understood by the host software. This occurs for example if there is some pass through operation while the system is in low power states. There are several strategies that may be used.

The first strategy allows the codec to reject power state transition requests (reporting PS-Error set) thus inhibiting the codec or just that specific widget from going into D3 when there is a dependency that the host software is not

aware of. In that case, s/w will have to re-issue a Set Power State verb to have to codec (or widget) transition in to D3 state at a later time and check the PS-Error bit again at that time. This does not ease the software burden as it does not provide knowledge as to how long this condition will remain. Thus there is a requirement for software to repeatedly attempt to command the codec in to D3, until it succeeds.

The preferred strategy is for the codec or widget to accept the D3 transition request and transition into D3 state, assuming that it is capable of servicing targeted pass-through operations while in D3 state. Servicing a pass through loop may require that certain logic in the codec remain powered up and functional in D3 state, at least for certain periods of time. This logic must operate independently of the HD Audio bus or controller, may be dynamically power managed (e.g. powered on or off) transparently to the HD Audio bus (e.g. based on activity on the loop through), and must not require any interaction with system software. The only exception to that may be the HD Audio bus clock (BCLK): if the codec requires BCLK to be available in D3 state, while a pass through loop is active, then it must indicate so by clearing the PS-ClkStopOk bit before entering D3 state, otherwise it must set that bit. Note, there is a requirement for the host software to check the state of ClkStopOk just prior to actually stopping the clock. This creates a small window, but which is handled by the codec not starting any non host software aware operation within 200ms after reporting that it is ok to stop the clock

#### All Power State (PS) fields are defined as follows:

| Valu              | e                                                                                                                                                                                         | General Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Active State (PS-                                                                                                                                                                                                                                                               | Set State (PS-                                                                                                                                                                        |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Bit 3<br>Reserved | Bits 2:0                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Act)                                                                                                                                                                                                                                                                            | Set)                                                                                                                                                                                  |  |

| Reserved,         | 000                                                                                                                                                                                       | <b>D0</b> fully on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Reports the actual                                                                                                                                                                                                                                                              | Always the value                                                                                                                                                                      |  |

| always 0          | <b>001</b> D1 allowing for some reduction but must return to D0 (Fully on) within 1 millisecond. Analog pass through circuits (e.g. CD analog playback) must remain fully on while in D1. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | power state of the<br>node and must be<br>the lower power<br>state of the                                                                                                                                                                                                       | set in the last Power State command or if no Power State                                                                                                                              |  |

|                   | 010                                                                                                                                                                                       | <b>D2</b> allows for (does not require) the lowest possible power consuming state from which it can return to the "fully on" state (D0) within 2 milliseconds. For modems, this is the "wake on ring" power state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Function Group power state and this node's power state.                                                                                                                                                                                                                         | command has<br>been received<br>since Power On                                                                                                                                        |  |

|                   | 011                                                                                                                                                                                       | D3 (or D3hot) allows for (does not require) lowest possible power consuming state under software control, in which EPSS requirements can be met, if EPSS is supported. Note that any low power state set by software must retain sufficient operational capability to properly respond to subsequent software Power State commands.  For any widgets that report EPSS of 1, they shall transition from D3 state to D0 state in less than 10 milliseconds. This is measured from the response to the Set Power State verb that caused the transition from D3 back to fully operational D0 state. This requirement must be met even if the Function Group or widget is in the process of transitioning in to a low power state, when it receives the Set Power State verb which commands it to transition back to D0 state.  It is permissible for the audio fidelity for analog outputs to be slightly degraded if audio rendering begins immediately once the fully operational state is entered. However, audio fidelity must not be degraded 75ms after the transitioning to D0 state  Note, if EPSS is not supported, then D3 state could potentially be identical to D3cold state | Nodes that support power states not supported by the Function Group must go to the next lower power consuming state supported by the Function Group. During transition from a lower power to a higher power consuming state this field reports the lower power consuming state. | or a Function Group Reset will be the default power state, which may be any power state supported by the node, other than D3cold. There is no requirement to be Fully on after reset. |  |

|                   | 100                                                                                                                                                                                       | D3cold is an optional state which allows for (does not require) lowest possible power consuming state under software control. A Function Group shall complete its transition to D3cold within 200ms from being commanded in to D3cold, with the exception of the link interface which shall remain alive, to allow the Function Group to receive a Get Power State verb and report D3cold as the Active state. When all Function Groups have reported transitioning in to D3cold state, the codec link interface shall power down, the codec will no longer respond to further                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | D3cold is different<br>than all other power<br>states, in that while<br>the codec (all<br>Function Groups) is<br>in D3cold, no<br>further commands<br>to the codec are                                                                                                          |                                                                                                                                                                                       |  |

| Value                  | General Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Active State (PS-                                                                                                                                                                   | Set State (PS- |  |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--|

| Bit 3 Bit Reserved 2:0 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Act)                                                                                                                                                                                | Set)           |  |

|                        | commands and power can be removed from the codec. No functionality (e.g. jack-detection) is required to be supported in this power state.  A Function Group can NOT be commanded out of D3cold state with a Set Power State verb. An exit from D3cold state occurs in the following conditions:  Power On Reset  De-assertion of link reset (synchronous with a link clock transition).  A Function Group can be taken out of D3cold with a double Function Group reset. Note that a Function Group can be taken in to and out of D3cold even when no link reset or Power On reset occurs.  Transition from this state back to D0 state must be complete within 200ms. Pops and clicks must be suppressed at -65dBFS or better on every transition to or from this state.  D3cold state can only be commanded to the Function Group. Behavior of this command to nodes other than the Function group, to enter D3cold state, is vendor unique and not specified by this specification. | possible. The codec will enter D3cold state only after s/w has polled the last Function Group which was commanded into D3cold and it has reported that it has entered D3cold state. |                |  |

**Table T1. Power State Field Definition**

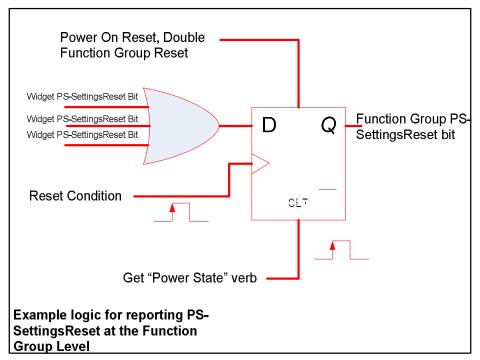

**PS-SettingsReset** is reported as set to one (1) when, during any low power state, the settings that were changed from the defaults have been reset to their default state. When settings have not been reset, this is reported as zero (0). The conditions that may reset settings to their defaults are:

- 1) Power On; always sets the PS-SettingsReset to one (1) for all widgets that report EPSS set to one (1) and that have host programmable settings and reset all settings.

- 2) Single Function Group Reset; sets PS-SettingsReset to one (1) for any widget that reports EPSS set to one (1) only if that widget's settings that should have been persisted were reset (changed) and follows Table T2.

- 3) Double Function Group Reset: sets PS-SettingsReset for all widgets that report EPSS set to one (1) and that have host programmable settings and resets all settings.

- 4) Link Reset; sets PS-SettingsReset to one (1) for any widget that reports EPSS set to one (1) only if that widget's settings that should have been persisted were reset (changed) and follows Table T2.

- 5) Clock stopped, causing dynamic logic to lose state, sets PS-SettingsReset to one (1) for any widget that reports EPSS set to one (1) for any setting that was changed.

- 6) Exit from D3cold always sets the PS-SettingsRest to one (1) for all widgets that report EPSS set to one (1) and that have host programmable settings, as power should have been removed to all these widgets by the codec logic.

The PS-SettingsReset bit for individual widgets, will be cleared to zero (0) on receipt of any "Set" verb to that widget; or After responding to a get Power State verb, to that widget, with the response containing PS-SettingsReset set to one (1).

The PS-SettingsReset bit for the Function Group is handled differently than at the widget level. For the Function Group the PS-SettingsReset is set to one (1) when any widget sets its PS-SettingsReset to one (1). The Function Group PS-SettingsReset bit is thus the logical "or" of all the EPSS bits, but is latched so that it can be reset independently and not require that all EPSS bits be reset.

Figure F1. Power State Field Definition

The PS-SettingsReset bit is 'sticky'. Once set, it will retain its value until it's cleared by a 'Get' verb, regardless of other single or double Function Group resets, Dx state transitions etc that may occur in the meantime.

It is strongly desired that settings that host software has changed from defaults not change across any Dx state transition, function group and link resets. Although there is no requirement to persist settings across power state transitions, and resets, re-populating these values, may add undue latency to restarting audio streams after low power state exits and resets.

The following table outlines how the handling of setting persistence should be performed across Dx states, clock stopping and resets. For codecs (function group) and widgets that do not reported EPSS set (1) compliance to this table is not required. When EPSS is reported, the use of PS-SettingsReset to report that settings have been reset (changed) is required.

Whenever the following table refers to 'Function Group Reset' or 'Function Group Resets' it means 'single Function Group reset/resets', unless it explicitly states 'double Function Group reset/resets'.

| Setting                      | Action across Dx                                                                                                                                                                                                                                           | Action with Link or                                                                                                                      | Codec, Function    |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

|                              | state transitions or                                                                                                                                                                                                                                       | Function Group reset                                                                                                                     | Group or Widgets   |

|                              | clock stopped                                                                                                                                                                                                                                              |                                                                                                                                          | that it applies to |

| Codec physical address (SDI) | Persist across Dx states, unless the link has been reset, in which case the codec shall initiate a Codec Initialization sequence to acquire an address when the link re-initializes. Note that unless the codec has been moved to a different SDI line the | Persist across Single and double FG reset but Link Reset will initiate a Codec Initialization to acquire an address from the controller. | Codec              |

<sup>&</sup>lt;sup>4</sup> Also note that, even though persisting codec parameters across power state transitions and resets is not a requirement of this specification, it is possible that some operating system vendors may require static register behavior and may not support the PS-SettingsReset bit

.

| Setting                                        | Action across Dx                              | Action with Link or                                                         | Codec, Function                              |

|------------------------------------------------|-----------------------------------------------|-----------------------------------------------------------------------------|----------------------------------------------|

|                                                | state transitions or<br>clock stopped         | Function Group reset                                                        | Group or Widgets that it applies to          |

|                                                | controller shall supply                       |                                                                             | that it applies to                           |

|                                                | the same address.                             |                                                                             |                                              |

| Converter Format; All bits                     | Persist across Dx states                      | Reset by POR, persist across                                                | Input & Output                               |

| [15:0] e.g. Type, Base,                        |                                               | Link & FG resets                                                            | Converters, Digital                          |

| Mult, Div, Bits Chan fields Converter Stream & | Reset to Default; must                        | Reset to default by all resets                                              | Converter Input & Output                     |

| Channel settings, all bits                     | not assume same                               | and does not set PS-                                                        | Converter, Digital                           |

| [7:0] e.g. Stream number in                    | stream is in operation                        | SettingsReset to one (1)                                                    | Converter                                    |

| bits [7:4] and Lowest                          | across Dx state                               |                                                                             |                                              |

| Channel number in bits [3:0]                   | transitions and could cause spurious audio to |                                                                             |                                              |

| [3.0]                                          | be played if not reset.                       |                                                                             |                                              |

| Digital Converter Controls                     | Persist across Dx states                      | Reset by POR, persist across                                                | Digital Converter                            |

| 1 &2, all bits                                 |                                               | Link & FG resets                                                            |                                              |

| Connection Select Index                        | Persist across Dx states                      | Reset by POR, persist across                                                | Input converter, Selector                    |

| values, all bits [7:0] Coefficients            | Vendor defined, but if                        | Link & FG resets  Vendor defined but if reset,                              | and Pin Complex<br>All                       |