#### Risk Factors

•Today's presentations contain forward-looking statements. All statements made that are not historical facts are subject to a number of risks and uncertainties, and actual results may differ materially. Please refer to our most recent Earnings Release and our most recent Form 10-Q or 10-K filing for more information on the risk factors that could cause actual results to differ.

•If we use any non-GAAP financial measures during the presentations, you will find on our website, intc.com, the required reconciliation to the most directly comparable GAAP financial measure.

#### Today's News

The world's first 3-D Tri-Gate transistors on a production technology

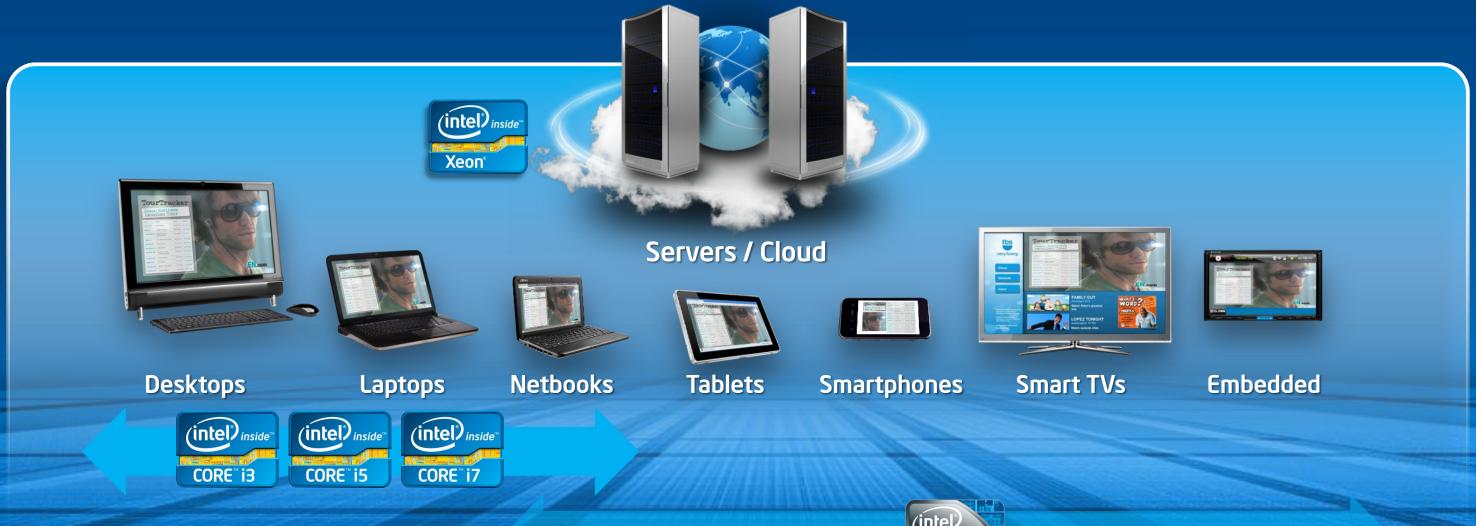

New 22nm transistors have an unprecedented combination of power savings and performance gains.

These benefits will enable new innovations across a broad range of devices from the smallest handheld devices to powerful cloud-based servers.

The transition to 3-D transistors continues the pace of technology advancement, fueling Moore's Law for years to come.

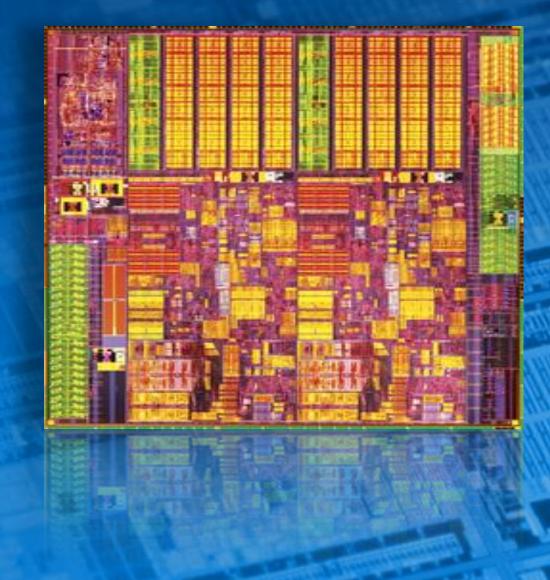

The world's first demonstration of a 22nm microprocessor -- code-named Ivy Bridge -- that will be the first high-volume chip to use 3-D Tri-Gate transistors.

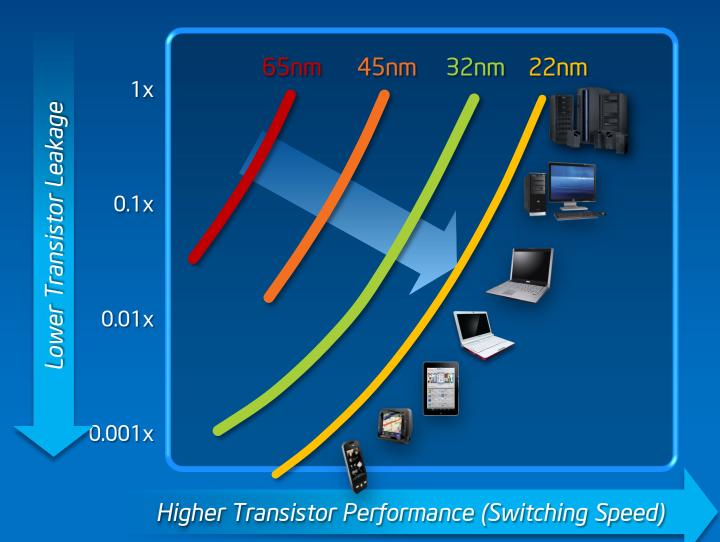

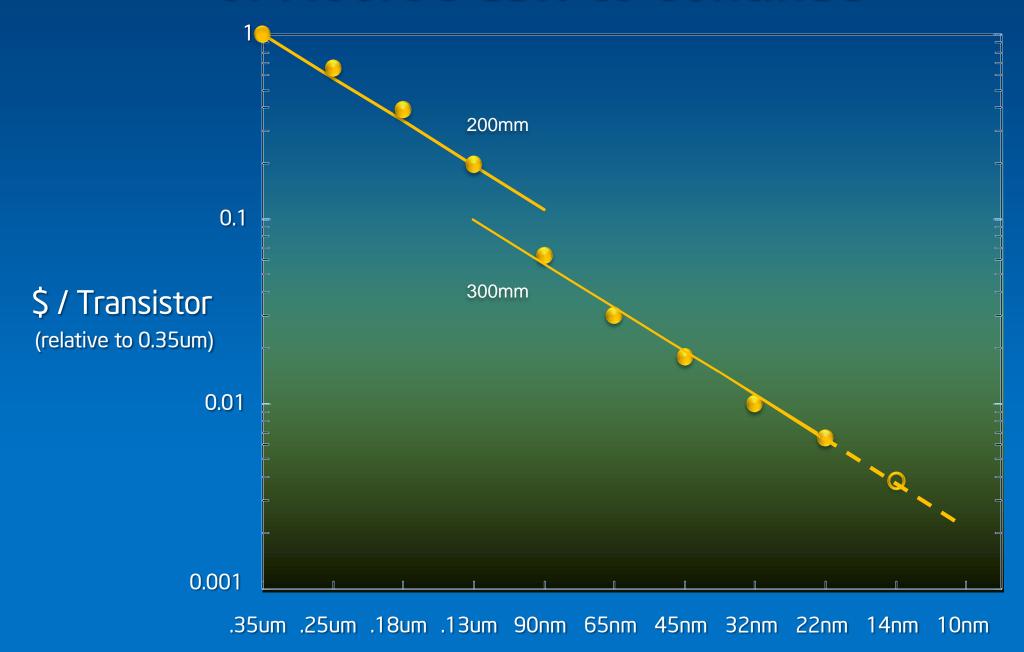

#### Energy-Efficient Performance Built on Moore's Law

Source: Intel

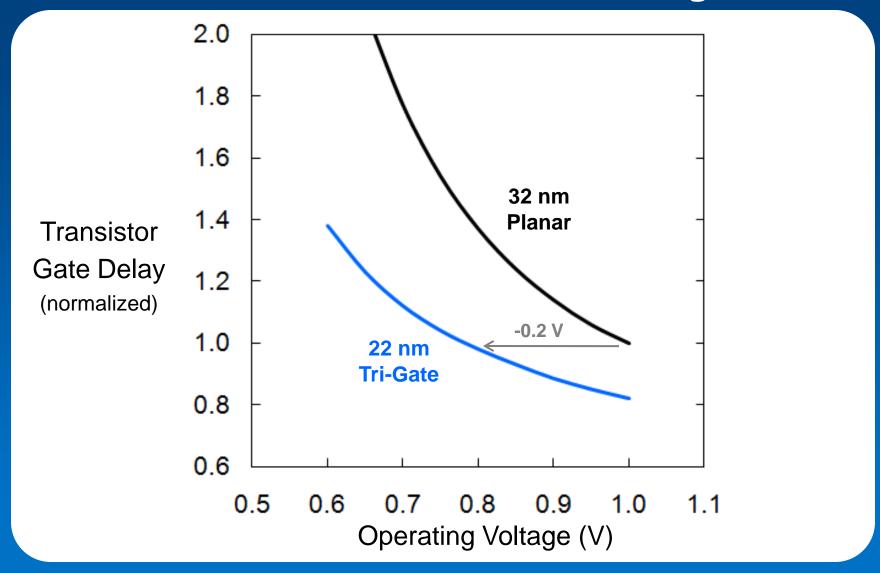

22 nm Tri-Gate transistors increase the benefit from a new technology generation

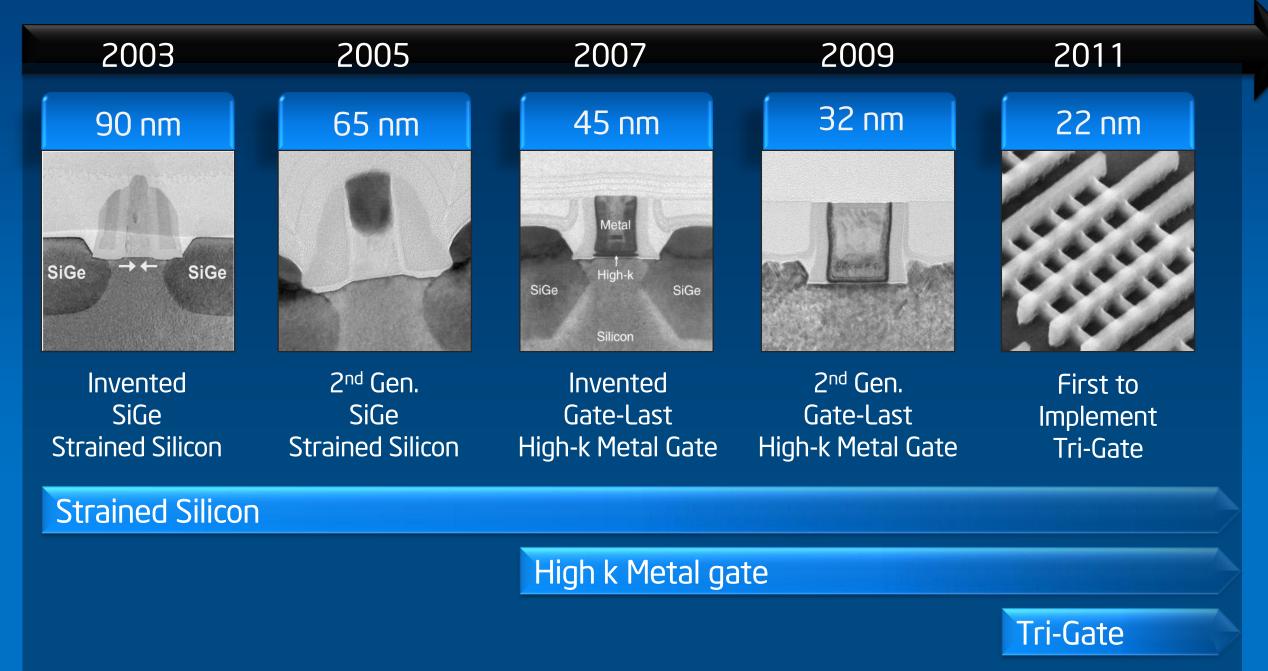

#### Transistor Innovations Enable Technology Cadence

# Transistor Innovations Enable Cost Benefits of Moore's Law to Continue

#### 22 nm Manufacturing Fabs

D1D -- Oregon

D1C -- Oregon

Fab 32 -- Arizona

Fab 28 -- Israel

Fab 12 -- Arizona

# Tri-Gate Achievement Results from Long Term Commitment to Research

Pathfinding

CEl transfer

Development

Tri-Gate Invented

Selected for 22nm node

2002

2003

2006

Pathfinding

CEl transfer

Manufacturing

Single-fin transistor demonstrated

Multi-fin transistor demonstrated

Tri-gate

SRAM cells

demonstrated

Tri-gate RMG process flow developed

Tri-gate optimized for HVM

Tri-Gate Mfg

Bringing innovative technologies to HVM is the result of a highly coordinated internal research-development-manufacturing pipeline

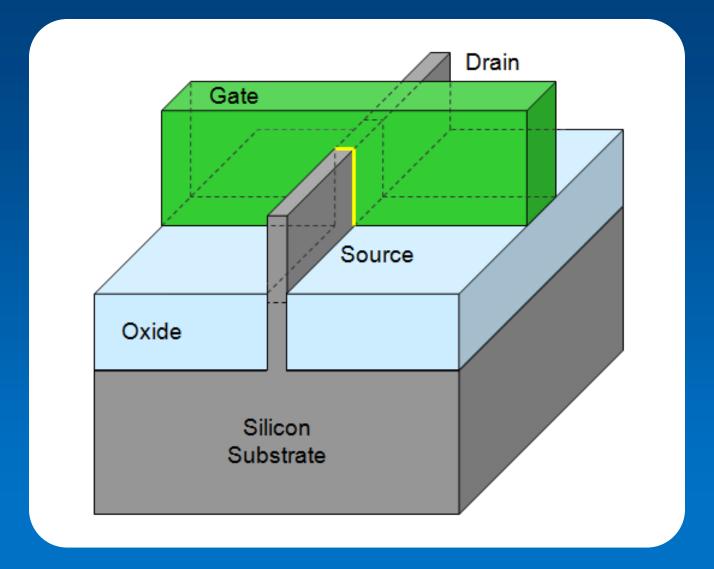

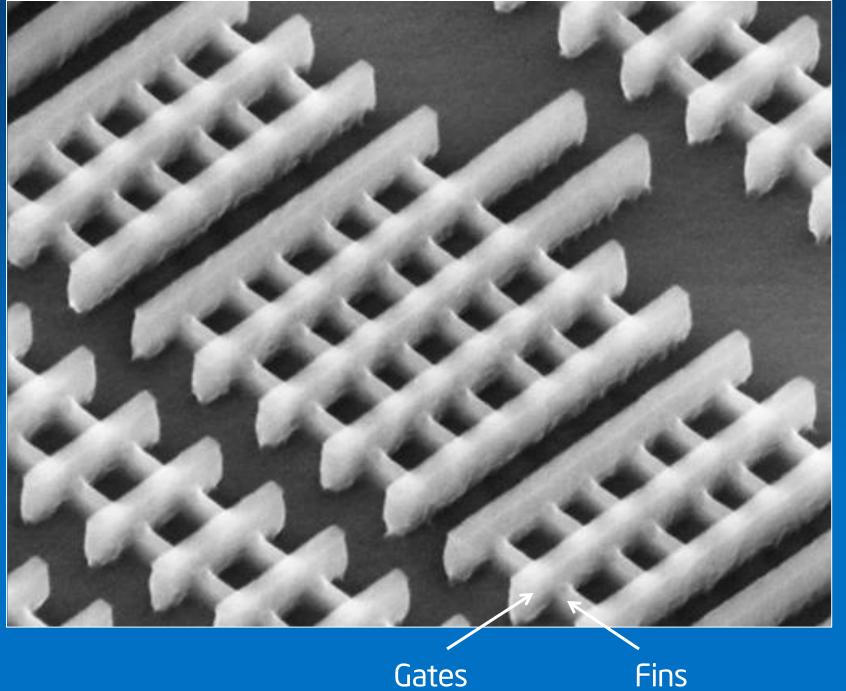

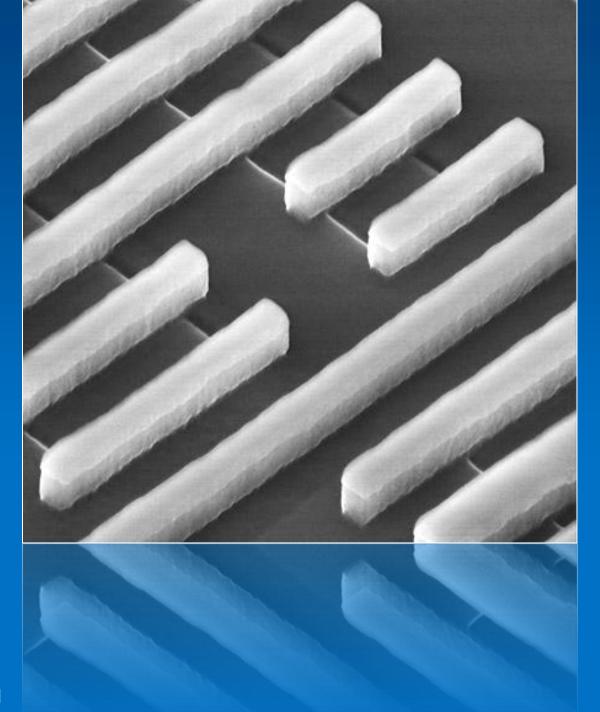

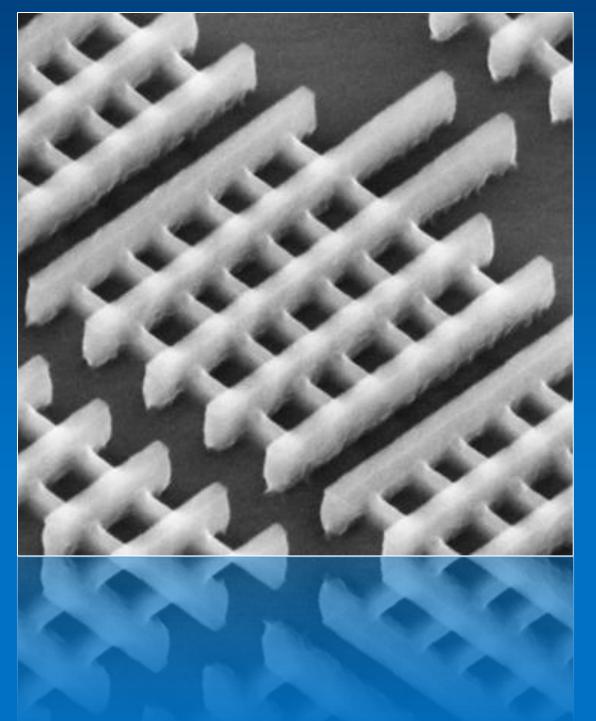

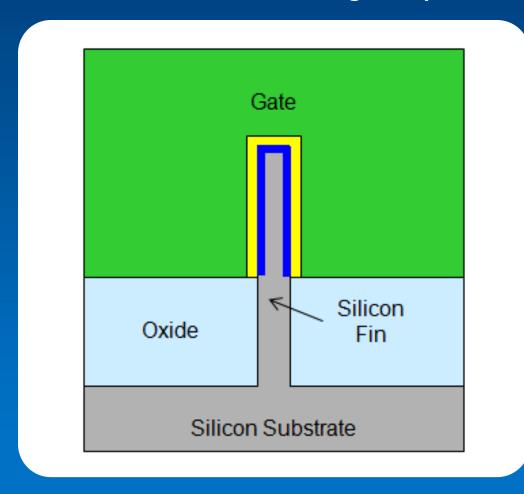

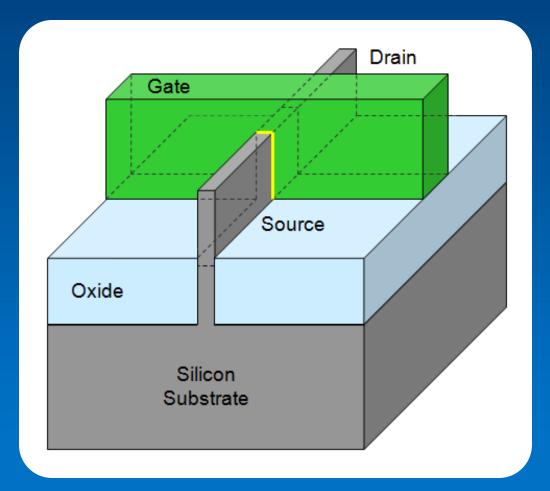

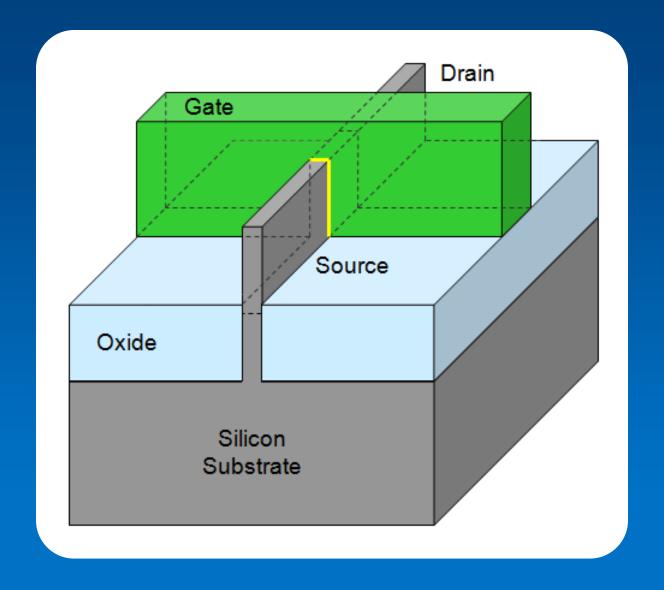

#### 22 nm 3-D Tri-Gate Transistor

3-D Tri-Gate transistors form conducting channels on three sides of a vertical fin structure, providing "fully depleted" operation

Transistors have now entered the third dimension!

### 22 nm 3-D Tri-Gate Transistor

#### 32 nm Planar Transistors

#### 22 nm Tri-Gate Transistors

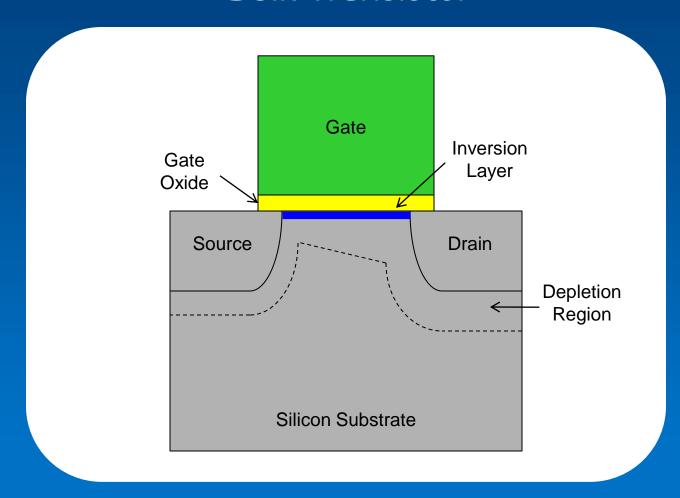

**Bulk Transistor**

"Transistor 101"

Substrate voltage exerts some electrical influence on the inversion layer (where source-drain current flows)

The influence of substrate voltage degrades electrical sub-threshold slope (transistor turn-off characteristics)

NOT fully depleted

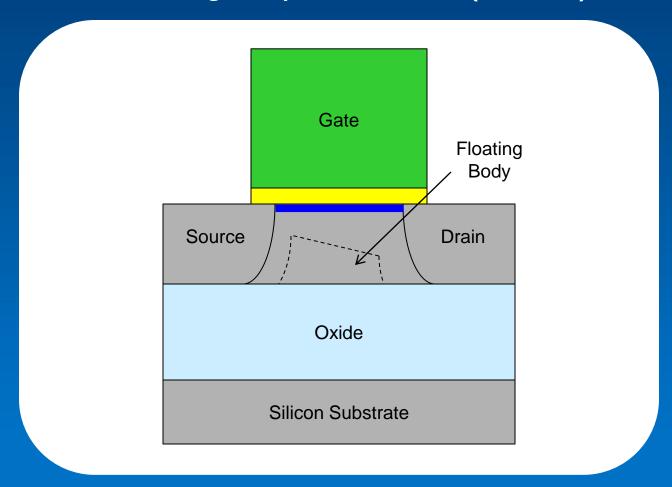

Partially Depleted SOI (PDSOI)

"Transistor 101"

Floating body exerts some electrical influence on inversion layer, degrading sub-threshold slope

NOT fully depleted

Not used by Intel

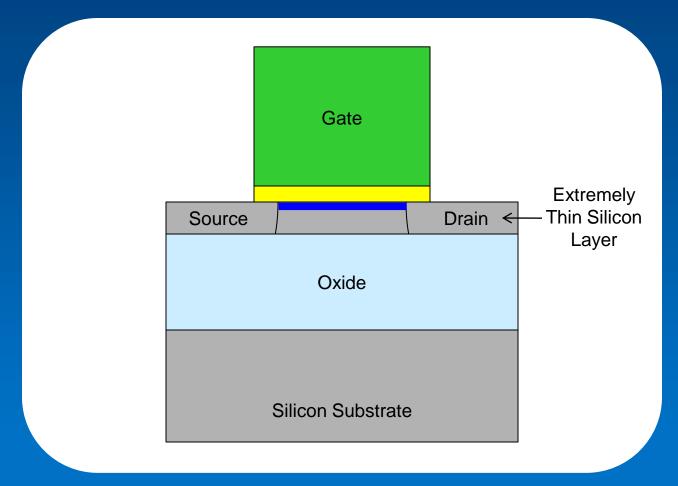

Fully Depleted SOI (FDSOI)

Floating body eliminated and sub-threshold slope improved

Requires expensive extremely thin SOI wafer, which adds ~10% to total process cost

Not used by Intel

Fully Depleted Tri-Gate Transistor

Gate electrode controls silicon fin from three sides providing improved sub-threshold slope Inversion layer area increased for higher drive current Process cost adder is only 2-3%

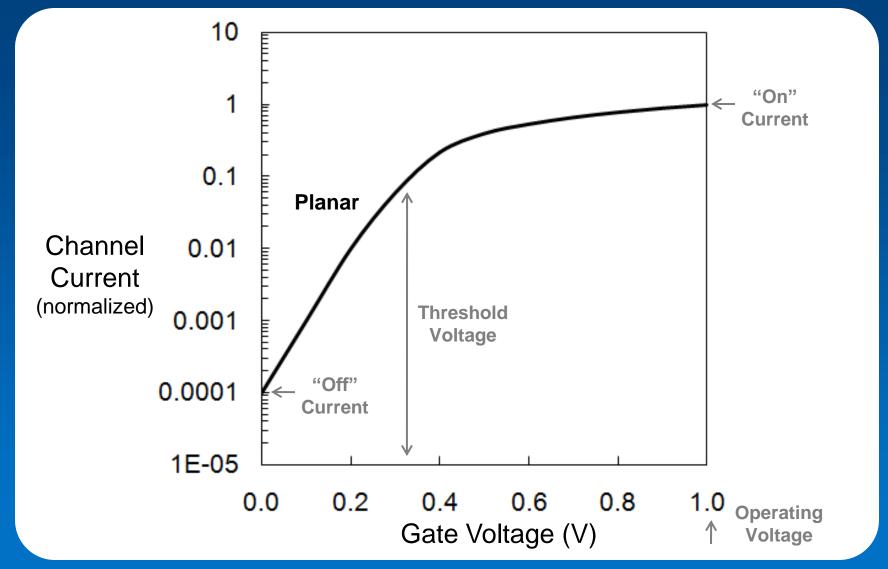

## Transistor Operation

"Transistor 101"

Maximize current in "on" state (for improved performance)

Minimize current in "off" state (for lower power)

Switch very quickly between the two states (for performance)

## Transistor Operation

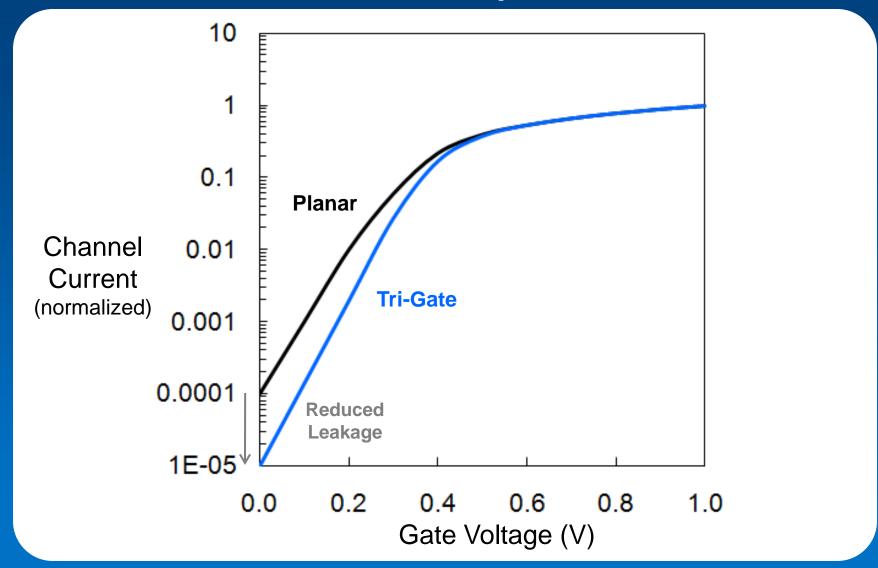

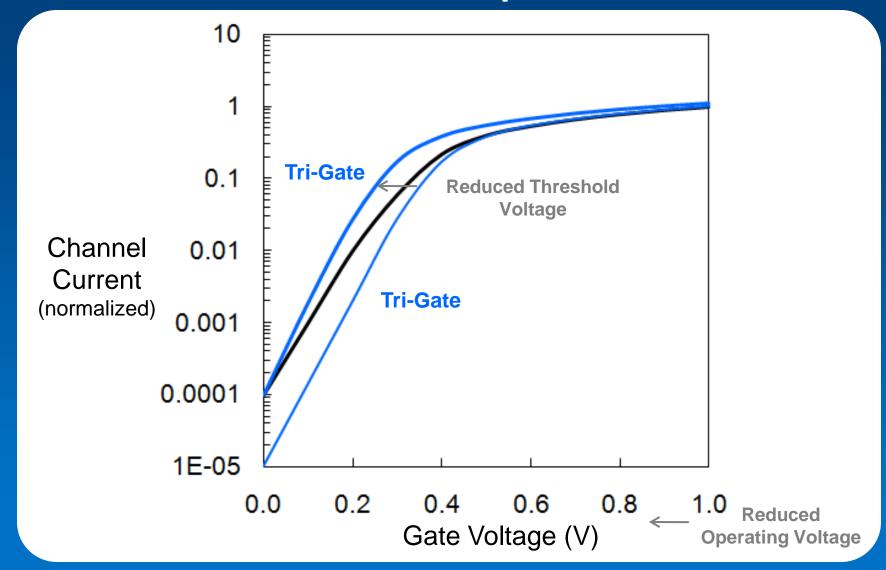

The "fully depleted" characteristics of Tri-Gate transistors provide a steeper sub-threshold slope that reduces leakage current

### Transistor Operation

The steeper sub-threshold slope can also be used to target a lower threshold voltage, allowing transistors to operate at lower voltage to reduce power and/or improve switching speed

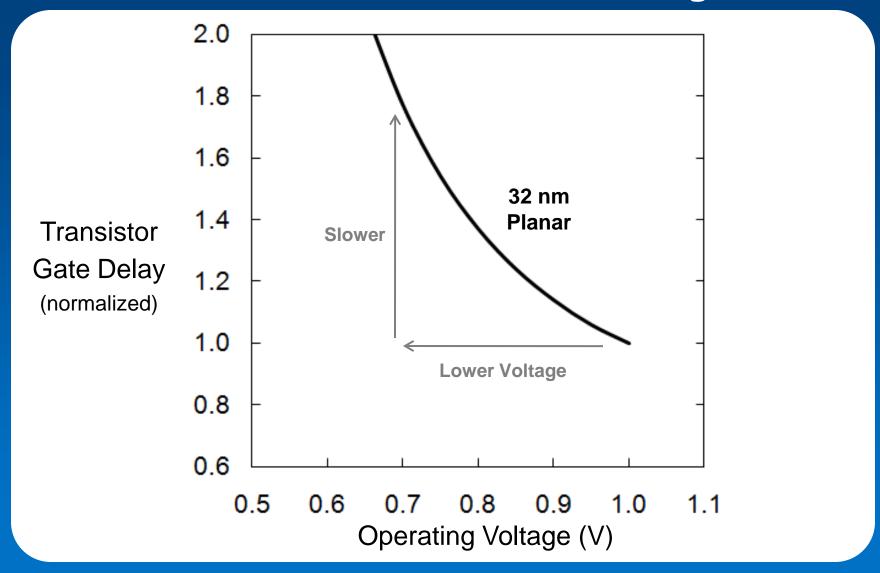

Transistor gate delay (switching speed) slows down as operating voltage is reduced

"Transistor 101"

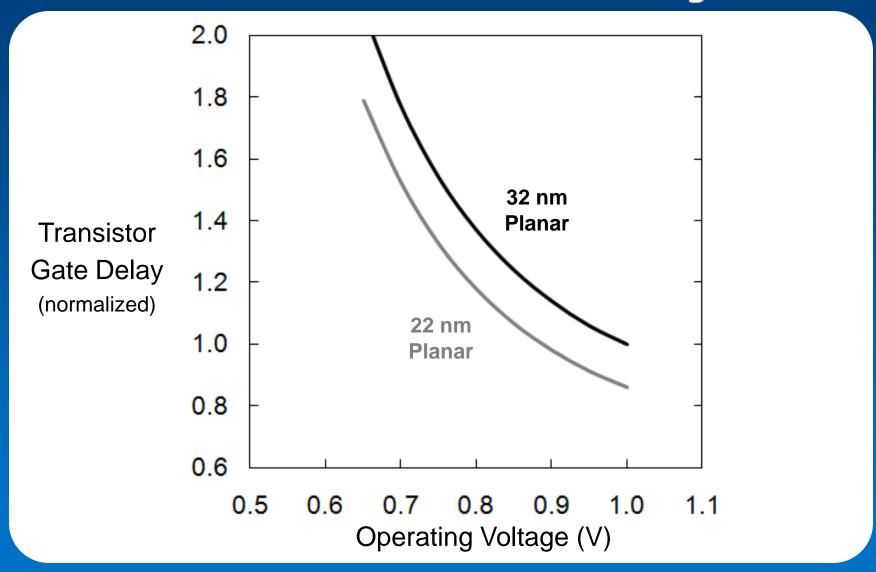

22 nm planar transistors could provide some performance improvement, but would still have poor gate delay at low voltage

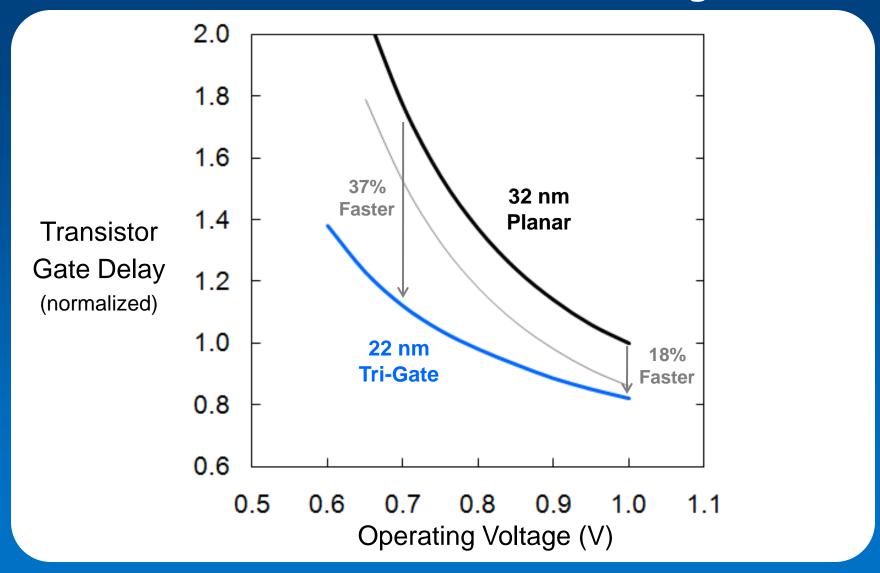

22 nm 3-D Tri-Gate transistors provide improved performance at high voltage and an *unprecedented* performance gain at low voltage

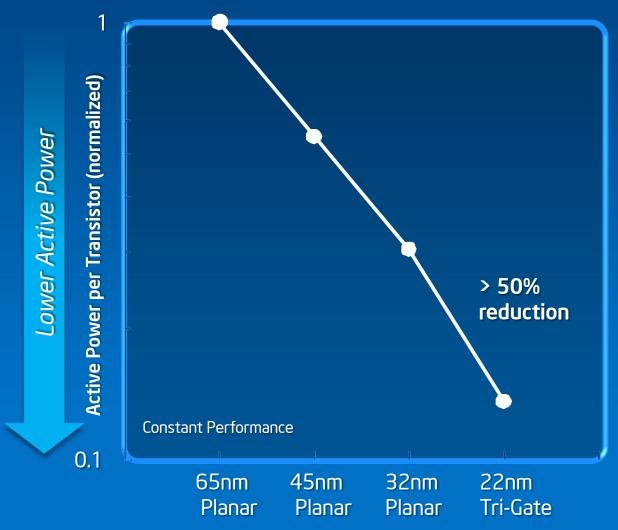

22 nm 3-D Tri-Gate transistors can operate at lower voltage with good performance, reducing active power by >50%

#### 3-D Tri-Gate Transistor Benefits

- Dramatic performance gain at low operating voltage, better than Bulk, PDSOI or FDSOI

- 37% performance increase at low voltage

- >50% power reduction at constant performance

- Improved switching characteristics (On current vs. Off current)

- Higher drive current for a given transistor footprint

- Only 2-3% cost adder (vs. ~10% for FDSOI)

3-D Tri-Gate transistors are an important innovation needed to continue Moore's Law

## 22nm Product Update

Dadi Perlmutter

Executive Vice President

General Manager,

Intel Architecture Group

#### 22nm Silicon Technology Breakthrough Benefits Broad Range of Intel Architecture Devices

New 22nm 3-D transistors deliver unprecedented performance improvement and power reduction for Intel's product portfolio

- This benefits smallest handhelds to powerful cloud-based servers

- 37% performance increase at low voltage vs. 32nm planar transistors\*

- Consumes only half the power at the same performance level as 2-D transistors on 32nm planar chips\*

## Intel Architecture Spans The Compute Continuum

#### Newest Manufacturing Technology Delivers Ivy Bridge

45 nm Process Technology 32 nm Process Technology 22 nm Process Technology

#### Penryn

Intel® Core™ Microarchitecture

TICK

#### Nehalem

NEW Intel® Microarchitecture

TOCK

#### Westmere

Intel® Microarchitecture (Nehalem)

TICK

#### Sandy Bridge

NEW Intel® Microarchitecture

TOCK

#### Ivy Bridge

Intel®

Microarchitecture

(Sandy Bridge)

TICK

Intel's First 22 nm Processor

Cadence of Innovation Delivers New Microprocessor Efficiency on the 22 nm Process

# Ivy Bridge Sandy Bridge Migrated to 22nm Process Technology

## Client: Efficient performance for thin and light form factors

- Increased performance vs. today's 2<sup>nd</sup> generation Intel<sup>®</sup> Core<sup>™</sup> product family

- Enhanced media and graphics performance with processor graphics

- Enhanced security features

## Server: Increased performance and improved efficiency

Integrated Storage Features

Further Demonstrating Intel Product and Process Leadership

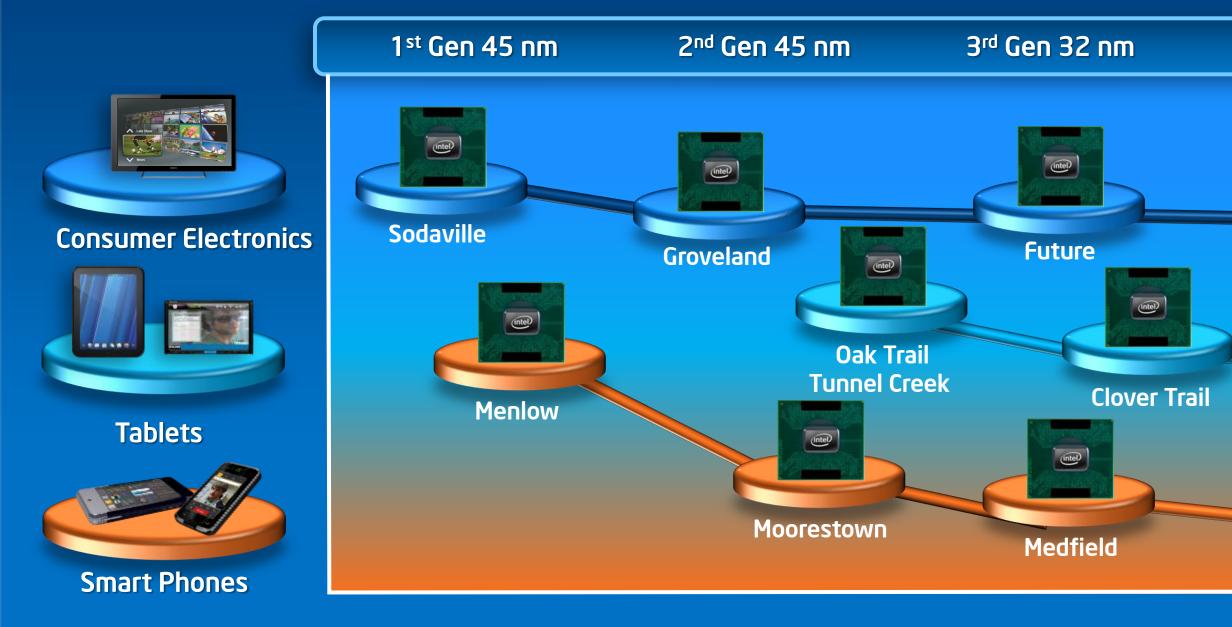

#### IA Platforms for Low Power Segments

Optimized Performance for Phones, Tablets, and Consumer Electronics

4<sup>th</sup> Gen 22 nm

**Future**

**Future**

**Future**

#### Legal Notices and Disclaimers

- INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL® PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. INTEL PRODUCTS ARE NOT INTENDED FOR USE IN MEDICAL, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS.

- Intel may make changes to specifications and product descriptions at any time, without notice.

- All products, dates, and figures specified are preliminary based on current expectations, and are subject to change without notice.

- Intel, processors, chipsets, and desktop boards may contain design defects or errors known as errata, which may cause the product to deviate from published specifications. Current characterized errata are available on request.

- Any code names featured are used internally within Intel to identify products that are in development and not yet publicly announced for

release. Customers, licensees and other third parties are not authorized by Intel to use code names in advertising, promotion or

marketing of any product or services and any such use of Intel's internal code names is at the sole risk of the user.

- Intel product plans in this presentation do not constitute Intel plan of record product roadmaps. Please contact your Intel representative to obtain Intel's current plan of record product roadmaps.

- Software and workloads used in performance tests may have been optimized for performance only on Intel

microprocessors. Performance tests, such as SYSmark and MobileMark, are measured using specific computer systems, components,

software, operations and functions. Any change to any of those factors may cause the results to vary. You should consult other

information and performance tests to assist you in fully evaluating your contemplated purchases, including the performance of that

product when combined with other products. For more information go to http://www.intel.com/performance

- Intel, Intel Inside, the Intel logo, Centrino, Centrino Inside, Intel Core, Intel Atom and Pentium are trademarks of Intel Corporation in the United States and other countries.

- Material in this presentation is intended as product positioning and not approved end user messaging.

- This document contains information on products in the design phase of development.

- \*Other names and brands may be claimed as the property of others.

- Copyright ° 2011 Intel Corporation, All Rights Reserved